- cross-posted to:

- riscv@lemmy.ml

- cross-posted to:

- riscv@lemmy.ml

cross-posted from: https://lemmy.ml/post/13412490

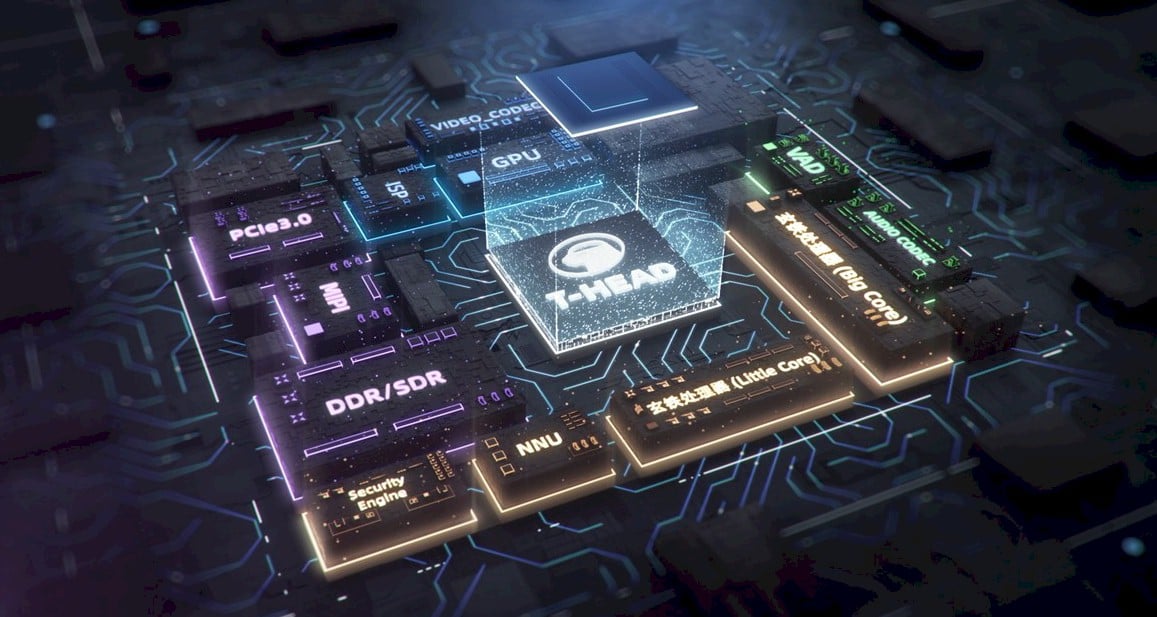

Alibaba’s research arm promises server-class RISC-V processor due this year

That’s an admirable goal, and I applaud the immense effort undertaken to make the OSS dream true.

The ISA may be open but I’m pretty sure the microarchitecture will be totally proprietary. Even with a kick ass microarchitecture they may still struggle if they can’t use the latest process nodes to actually manufacture the chips.

Having said that I suspect the main challenge RISCV is going to face is the software ecosystem. That stuff can take a decade to build and requires a degrees of cooperation between all the companies building chips.

I don’t think they’re doing this for oss reasons

I don’t think they’re even required to publish the design, they could keep it proprietary

They’re not. They’re doing it because they fear being SOL if America/the West enforces more sanctions on things like ARM chips/designs or Intel, etc.

And yes, IIRC RISC-V is MIT licensed or something close. Basically companies can take it and implement whatever on top and not have to contribute back.

Alibaba’s research arm

server-class RISC-V processor

Is this on purpose?

ARM is a type of RISC

V, it makes sense their ARM division expands to other RISCVarchitectures.EDIT: ARM is a type of RISC, not RISCV

No it’s not. Arm is a RISC architecture. RISC-V also is a RISC architecture.

Arm is explicitly not RISC-V.

With all the liberty to do some research before commenting, I’m rather disappointed to see such factually wrong comment.

I did, I just accidentally wrote RISCV instead of RISC. The acronym ARM actually stands for “Acorn RISC Machine”. TheLowSpecGamer has an interesting animated series about it’s development that is worth checking out.

Here is an alternative Piped link(s):

Piped is a privacy-respecting open-source alternative frontend to YouTube.

I’m open-source; check me out at GitHub.

Don’t you mean ARM is a type of RISC? (RISC = Reduced Instruction Set Computer)

Yes, I somehow wrote RISC-V instead of RISC 😅. You’re right.

Arm in this context doesn’t mean ARM.

I can see where this came from. ARM and RISC-V are both reduced instruction set computer (RISC) architechtures but are not the same. Arm is a proprietary ISA originally from Acorn. Risc-v is a new ISA developed completely open-source

EDIT: also, not to be killjoy, but for clarity “research arm” means apendage or division and is completely unrelated

I disagree. The simplest and best reading is they have an ARM CPU for research, and the CPU produced the RISC-V design.

Maybe we’re reading something different, or this is tongue and cheek but "Alibaba’s research arm, the Damo Academy, " sounds like research arm is a synonym for “research division” or “research department”.

Nope, definitely a CPU. It’s the CPU that’s promising the server-class RISC-V processor.

Where in that article do you read that?

The part where it says “arm.”

You’re really not getting the sarcasm here are you…

Is it going to have IME equivalent or will this thing actually be safe?

RiscV has been used for small specific tasks but running a whole OS on it still seems far fetched with so many libraries being unsupported. (yes it exists already but that is also very limited in functionality)

You can run desktop linux on RISC-V. https://youtu.be/1apoFXZ9ad8?si=DMF37jRfUqRHRDm9

Here is an alternative Piped link(s):

https://piped.video/1apoFXZ9ad8?si=DMF37jRfUqRHRDm9

Piped is a privacy-respecting open-source alternative frontend to YouTube.

I’m open-source; check me out at GitHub.